高速RCP技术

传统基于实时操作系统的CPU核运行控制算法,因为CPU性能强大,拥有强大的计算能力, 但同时会因为实时操作系统的指令响应、系统的基础负荷、系统长时间运行的抖动、CPU与FPGA之间总线交互的延迟等问题,导致基于实时操作系统的CPU一般难以运行20K以上的控制代码,因此,其适用于计算负担重、闭环速度要求不高的场合。

随着电力电子开关频率的不断提高,一些基于瞬时值控制等场合,提出了更高的控制速率(>20kHz)要求,传统基于实时操作系统的RCP因为以上原因,很难应用于高速控制应用。

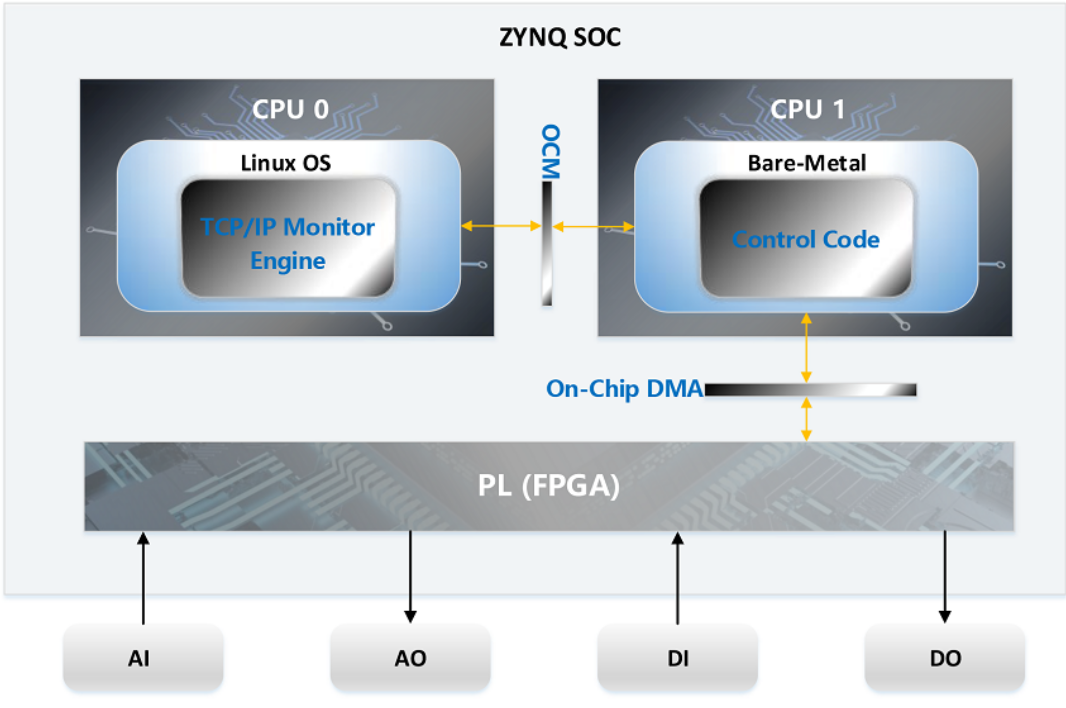

高速RCP架构与原理

全新的高速RCP基于ZYNQ SOC 架构如下图所示(CPU和FPGA同一个芯片),利用SOC架构可实现FPGA和CPU之间短至1-2us的传输时间,双核CPU1个CPU核负责通信等1个CPU核专注控制算法运行,同时专注控制算法运行的CPU核采用Bare-metal(裸核)的技术替代实时操作系统的技术,充分利用Bare-metal的无OS Overhead、高确定性的优势,来实现高达50K的控制算法运行。

高速RCP技术优势

1. 基于ZYNQ SOC 架构,实现超低延时

2. 采用Bare-metal技术,实现高实时性和高确定性

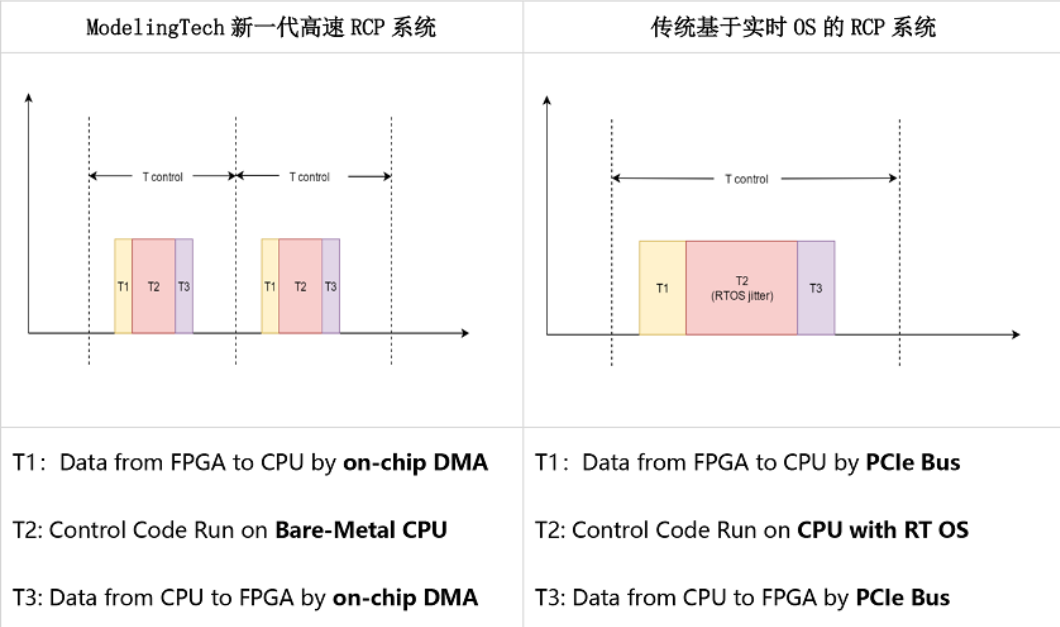

新一代高速RCP架构 VS 传统RCP架构

RCP架构 低延时测试

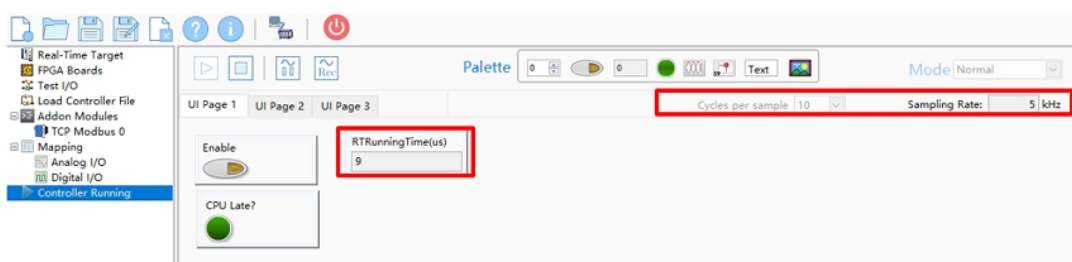

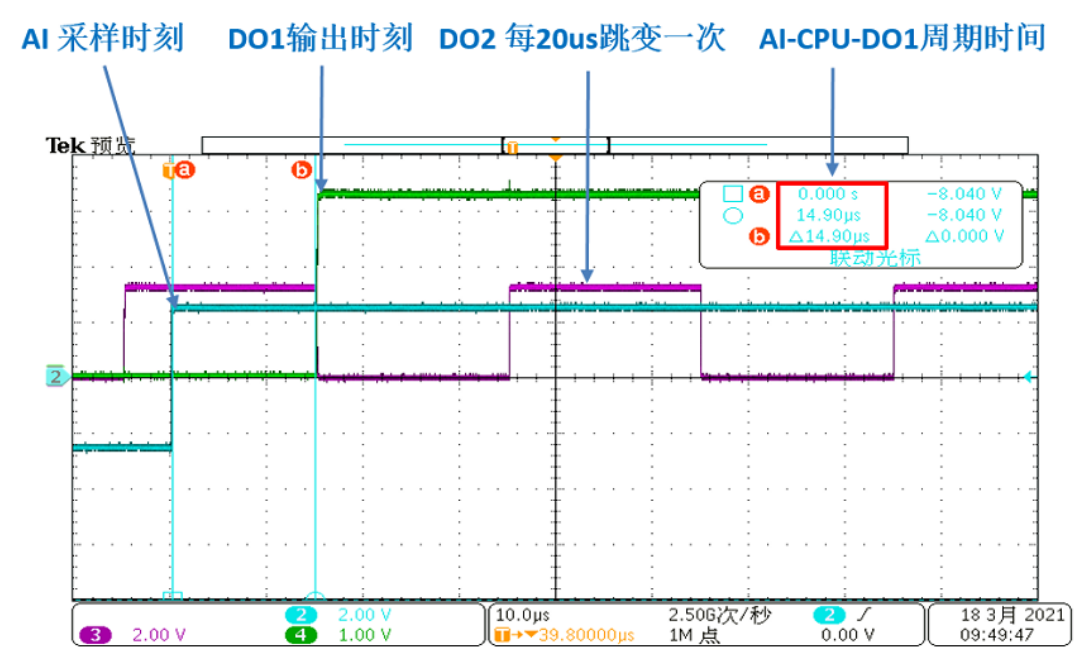

控制程序按20us( 50kHz)周期实时运行:

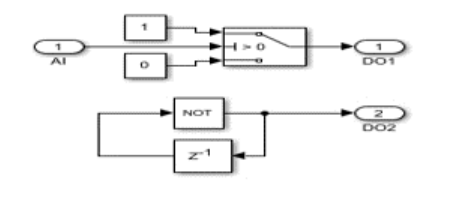

注:控制程序代码中包含如下程序:

可以观察得到:

· 控制系统严格按20us周期运行,AI-CPU-DO整个过程用时大约为14.9us,系统有5.1us空余时间片;

· CPU耗时9us,包含算法运行时间、双核的交互、算法的IO映射等;

· FPGA->CPU, CPU->FPGA,上传下行和信号更新等基础负担大概用时5.9us。

基于Bare-Metal的高速RCP VS 基于实时OS 的RCP

高速RCP应用实例

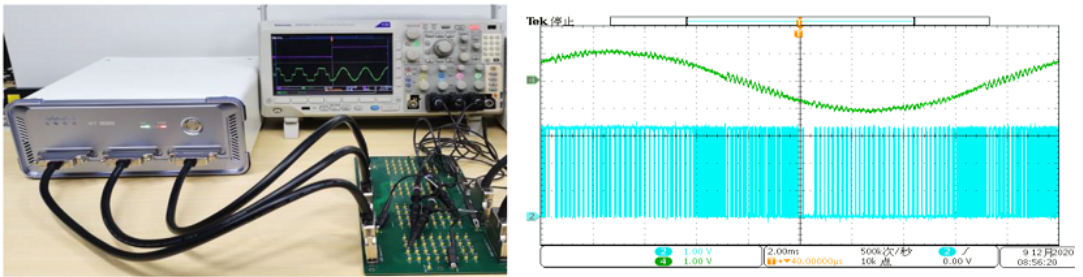

50kHz 有源滤波控制

• 左图里蓝色设备为MT 1050 RCP控制器,它以20us步长运行APF控制程序

• 左图中的示波器图片可以看到使能滤波后(紫色为使能信号),梯形的电网电流经过补偿变为了正弦波

• 右图是此系统运行时示波器图片,上面曲线为电网电流一个周期,下面曲线为50kHz的PWM波